FlexSPI使用AHB命令访问 手册1680页

- 作者: Kobe小东

- 来源: 51数据库

- 2021-06-27

27.5.10 AHB命令访问Flash

在AHB地址空间0x60000000-0x80000000上,AHB总线可以直接访问Flash。这个地址空间映射到FlexSPI中的串行闪存。AHB总线访问这个地址空间可能需要触发Flash访问命令序列。

对于串行闪存的AHB读取访问,FlexSPI将从闪存中获取数据到AHB RX缓冲区,然后在AHB总线上返回数据。对于AHB对串行的写访问,FlexSPI将缓冲AHB总线写入的数据到AHB TX缓冲区,然后再传输到串行闪存。?

对AHB命令方式来说,除了FlexSPI的初始化,不需要软件配置或轮询。AHB master 透明地访问外部闪存设备类似于正常的AHB Slave。

AHB命令通常用于访问串行闪存空间。IP命令通常用于访问外部闪存器件中的控制寄存器和状态寄存器或OTP等其他空间。

以下段落描述AHB 命令方式读写操作的细节。注意当FlexSPI控制器返回AHB总线错误的SFM访问,AHB master 该停止在当前突发访问下的节拍。

27.5.10.1 AHB对Flash的写访问

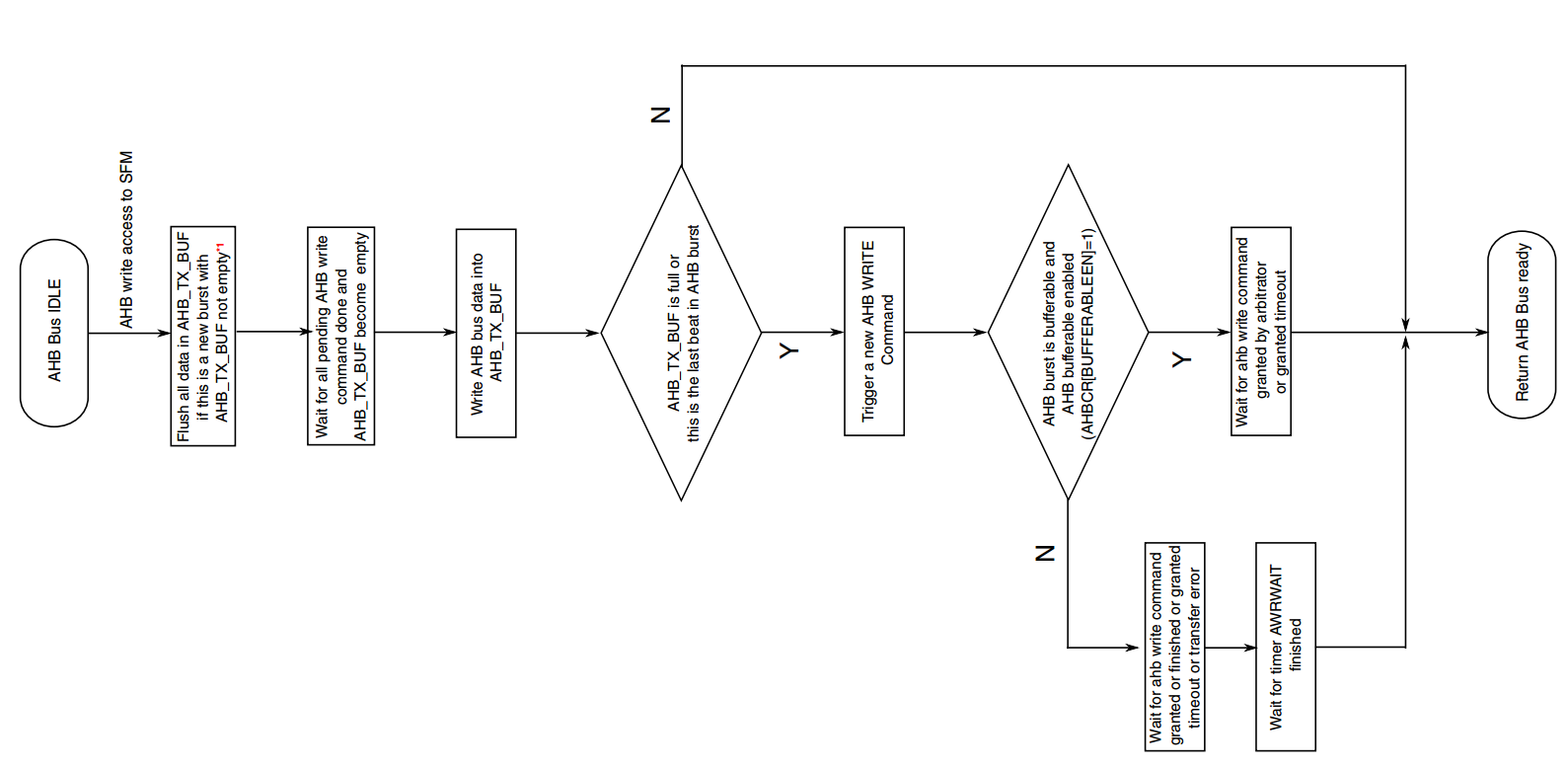

对于Flash的AHB写访问,FlexSPI将AHB总线的写数据缓冲到内部的AHB TX缓冲区,然后传输给Flash。FlexSPI只缓冲一个AHB突发写数据。下图显示了硬件操作对AHB对Flash的写访问的响应。?

?

在以下情况下,FlexSPI触发新的AHB写命令:

这个节拍是当前AHB脉冲(除INCR以外的任何脉冲类型)中的最后一个节拍。

AHB TX缓冲区在缓冲当前节拍数据后已满。

AHB总线变成空闲的或者一个新的突发且AHB TX缓冲区非空。

关于触发AHB写命令的详细信息:

Flash访问开始地址:

由AHB决定的突发地址。FlexSPI将在AHB TX缓冲区中记录数据的开始地址,这个地址将用作flash访问的开始地址。

? ? ? ?

闪存片选:

FlexSPI通过闪存访问开始地址和闪存大小来 确定芯片选择(通过地址区分使用哪个片选信号)。

?闪存命令序列索引:

由FLSHxCR2 [AWRSEQID]寄存器决定。

闪存命令序列号:

由FLSHxCR2[AWRSEQNUM]寄存器决定。如果AWRSEQNUM非零,每次AHB 写命令时都会触发多个flash访问命令序列。

LUT中从AWRSEQID到(AWRSEQID+ AWRSEONUM)索引的序列将依次执行。

闪存访问模式(单独/并行):

由AHBCR[APAREN]决定。

闪存的数据大小:

由AHB TX缓冲区中缓冲数据的字节数决定。

下面的示例说明了AHB对Flash的写访问的内部逻辑。

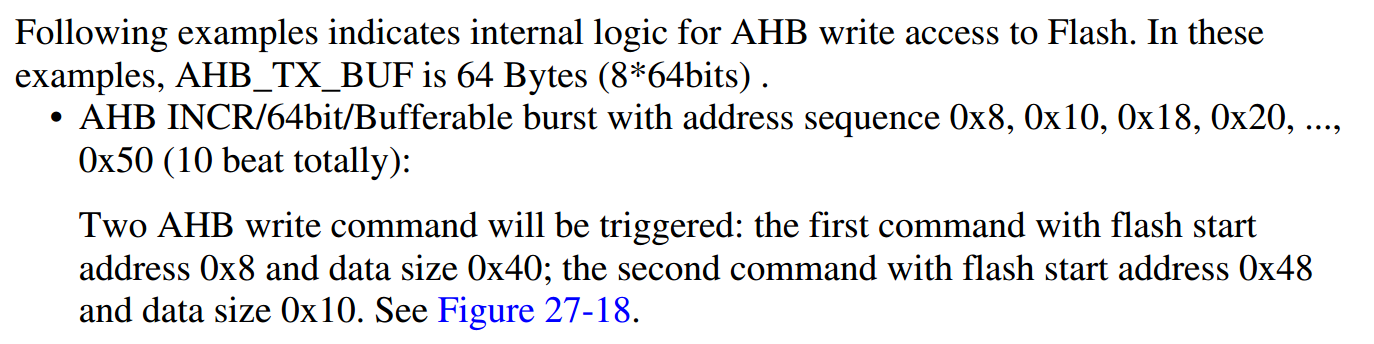

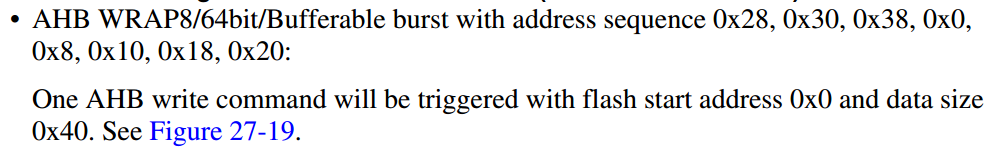

在这个例子中,AHB TX BUF是64字节(8*64位)。AHB INCR/64位/可缓冲的突发地址序列0x8,0 x10,0 x18, 0 x20,…0x50 (共10 节拍):

两个AHB写命令将被触发:第一个命令flash启动地址是0x8,数据大小是0x40;第二个命令的flash启动地址是0x48,数据大小是0x10。参见图27-18。

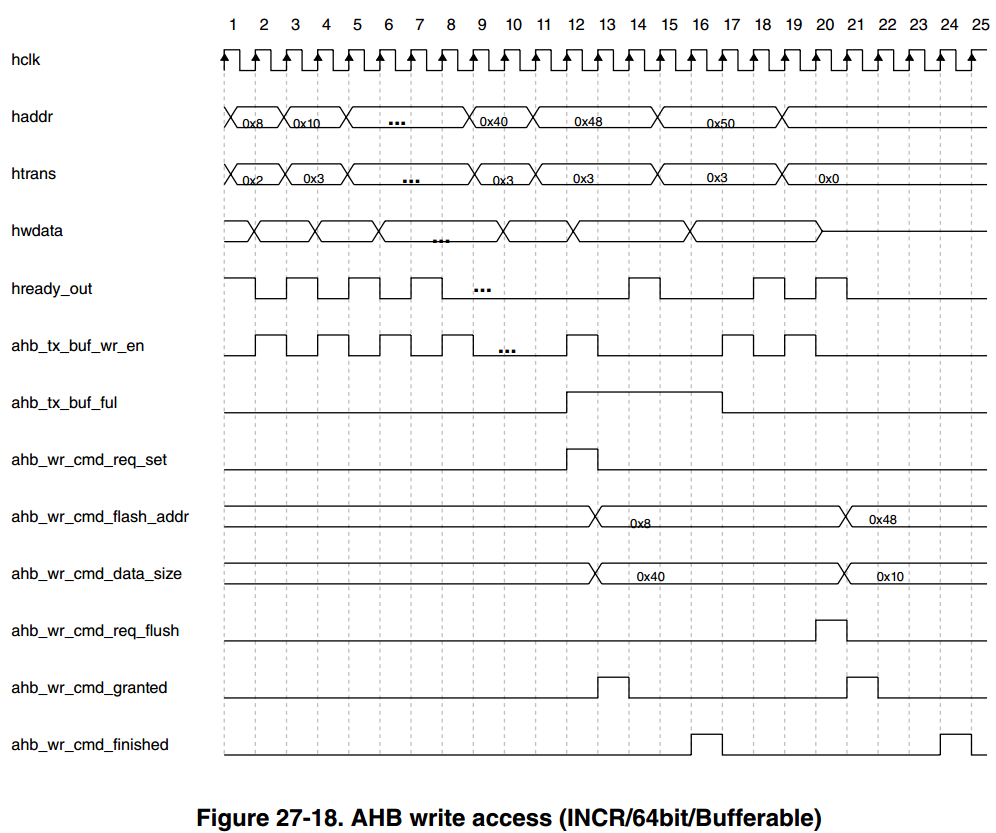

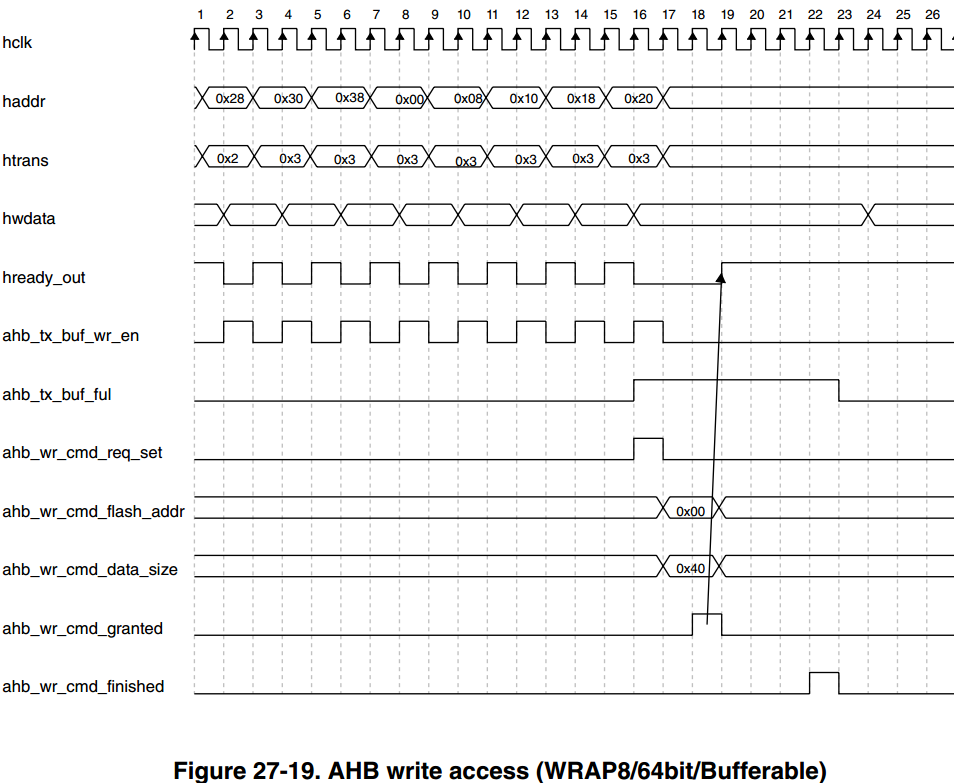

AHB WRAP 8/64bit/可缓存突发传输,地址序列为0x28, 0x30, 0x38, 0x0,0x8. 0x10、 0x18、 0x20:

一个AHB写命令将被flash启动地址0x00和数据大小0x40触发。参见图27-19。?

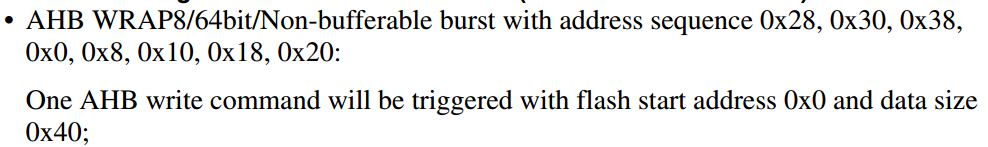

?AHB WRAP8/64bit/非缓存突发传输,地址序列是0x28, 0x30, 0x38。0x0、0x8、0x10、0x18、0x20:

?AHB WRAP8/64bit/非缓存突发传输,地址序列是0x28, 0x30, 0x38。0x0、0x8、0x10、0x18、0x20:

一个AHB写命令将被flash启动地址0x00和数据大小0x40触发

?

?

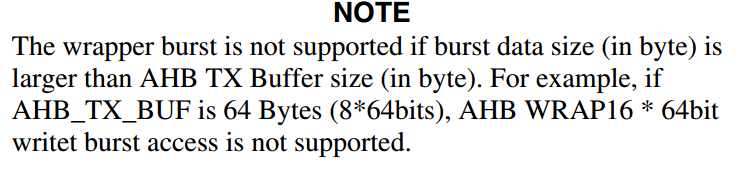

注意:

如果突发数据大小(以字节计)大于AHB TX缓冲区大小(以字节计),则包装器突发传输不受支持。

例如,如果AHB_TX_BUF 是 64 字节 (8 * 64 位), AHB WRAP16 * 64 位突发传输写入不受支持。

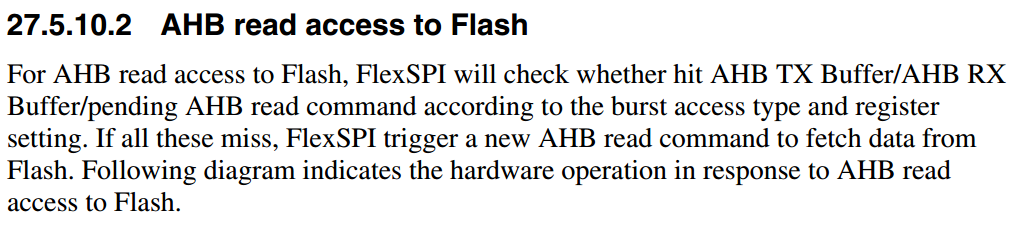

27.5.10.2 AHB对Flash的读访问

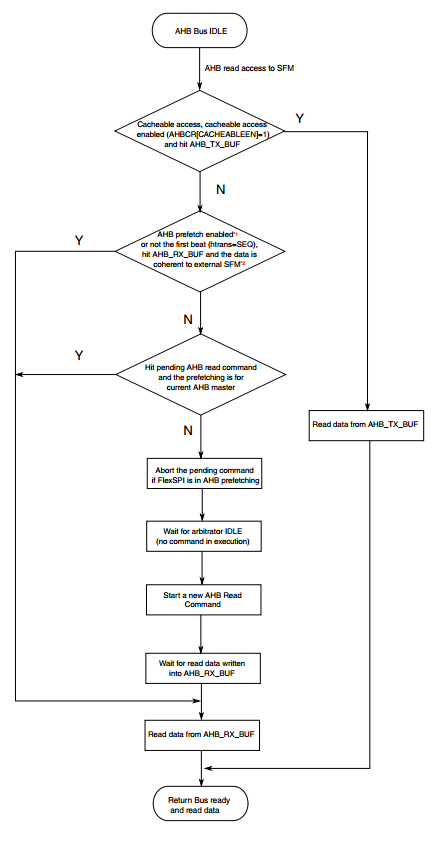

对于Flash的AHB读访问,FlexSPI会根据突发访问类型和寄存器设置来检查是否命中AHB TX Buffer/AHB RX Buffer/pending (等待)AHB读命令。如果所有这些都失败了,FlexSPI将触发一个新的AHB read命令来从Flash中获取数据。下图显示了硬件操作对AHB读访问Flash的响应。

注意:

1. AHB预读取启用时,AHBCR[PREFETCHEN] = 0x01和AHBRXBUFxCR0[PREFETCHEN] = 0x01,(x是当前ahb主缓存的ahb rx buffer ID)。

2. AHB RX缓冲区保存从Flash读取的数据。如果AHB写入同一个flash地址,这些数据可能变得不连贯。

触发AHB读命令的详细信息

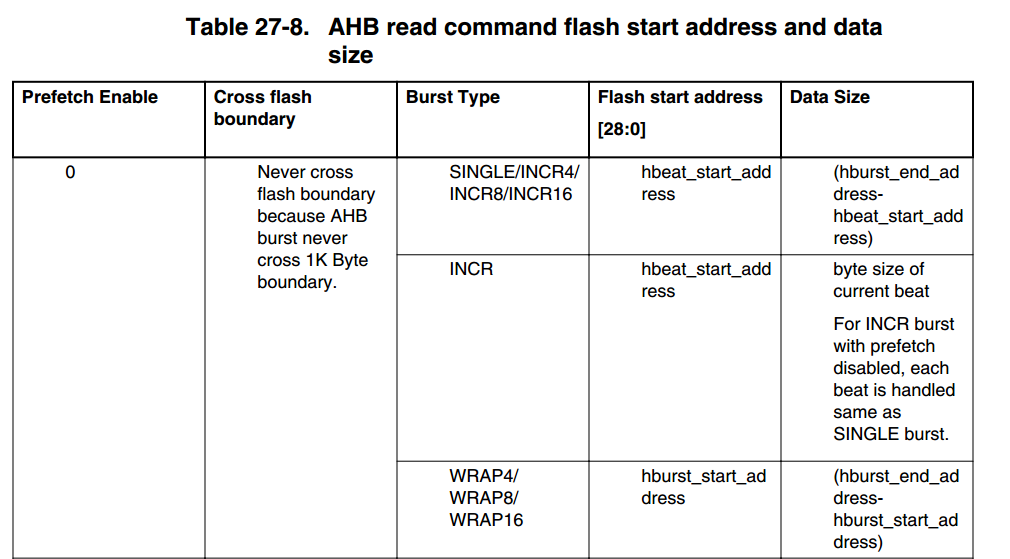

Flash 访问起始地址和数据长度:

由AHB地址,突发类型和突发传输大小决定。FlexSPI将从当前节拍的起始地址处获取数据。

注意:

hbeat_satrt_address 是从AHB master 当前节拍中的 HADDR?

hbeat_satrt_address是当前突发传输的最低地址;hbeat_end_address是当前突发传输脉冲1的最高地址。例如,WRAP4 突发传输的HADDR有 0x08,0x0c,0c00,0x04。

ahb_rx_buf_sz 当前主控使用的AHB RX BUF 字节大小。

flash_top_address 是当前访问的flash器件的top地址。

片选:

FlexSPI的片选信号由起始地址和访问大小确定。

Flash命令序列索引:

由FLSHxCR2[ARDSEQID] 确定

Flash命令序列号

由FLSHxCR2[ARDSEQNUM]确定。如果ARDSEQNUM非零,每次AHB 读命令都会触发Flash访问命令序列。在LUT中的序列索引从ARDSEQID到ARDSEQID+ARDSEQNUM将会被执行。

Flash访问模式(单独/并行):

由AHBCR[APAREN]决定。

注意:

FlexSPI确定哪些ARDSEQNUM/ARDSEQID字段将被flash设备芯片选择自动用作序列ID。更多细节请参考MCR2[SAMEDEVICEEN]。

FlexSPI确定哪个AHB RX缓冲区用于当前读取访问主ID。有关的更多细节AHB RX缓冲区ID和AHB主ID映射,引用AHB RX缓冲区管理。

不允许分配AHB RX缓冲区小于AHB突发大小。在这个案例中这种行为是未知的

27.5.10.3 AHB RX缓冲区管理

有4个缓冲区(缓冲区0 -缓冲区3)在AHB RX缓冲区,这对AHB master来说是透明的(不需要由AHB master管理)。FlexSPI获取flash数据并在AHB总线上自动返回。没有状态寄存器轮询需要AHB读访问串行闪存。

AHB Rx缓冲区的总大小为1K字节。缓冲区大小是由每个缓冲区在AHBRX缓冲区的AHBRXBUF0CR0[BUFSZ]-AHBRXBUF6CR0[BUFSZ]寄存器字段灵活配置的

缓冲区0到缓冲区3的缓冲区大小可以设置为0。如果缓冲区大小设置为0x0,那么FlexSPI将忽略相关的MSTRID字段设置(在同一个AHBRXBUFxCR0寄存器中)。缓冲区3是用于所有没有分配到缓冲区0-缓冲区2的AHB master。FlexSPI忽略Buffer 3 size设置字段(AHBRXBUF3CR0[BUFSZ]),其Buffer size为:AHB RX Buffer 总大小?减去??(Buffer 0 到Buffer 2 )的和。

当有AHB读访问串行闪存,FlexSPI决定哪个AHB RX缓冲区使用如下:

1. 如果主ID为AHBRXBUF0CR0[MSTRID],且AHBRXBUF0CR0[BUFSZ]不为零,则使用缓冲区0

2. 如果主ID = AHBRXBUF1CR0[MSTRID]和AHBRXBUF1CR0[BUFSZ]不为零,缓冲区1将被使用

3.如果主ID为AHBRXBUF2CR0[MSTRID]且AHBRXBUF2CR0[BUFSZ]不为零,则使用缓冲区2.

4 如果以上情况不符合,将使用缓冲区3

注意:

软件应该确保每个缓冲区的缓冲区大小不小于AHB使用这个缓冲区的主读取访问的最大突发大小。否则,行为是未定义的。

不支持为单个AHB master 分配多个缓冲区。

当AHB读取预取启用时(AHBCR[PREFETCHEN]置位),预取数据大小“将由缓冲区大小决定。如果没有Flash边界,FlexSPI将从外部Flash获取数据与缓冲区大小。

AHB主优先级设置(寄存器字段AHBRXBUFxCR0[priority]仅用于AHB预取的挂起控制。参考“中止和暂停”命令。

?